具体描述

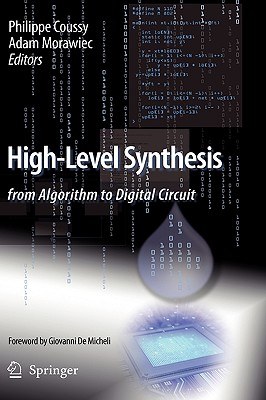

《集成电路设计与验证:从系统级到门级》 书籍简介 本书旨在为电子工程、计算机科学以及相关领域的专业人士和高年级学生提供一套全面而深入的集成电路(IC)设计与验证的知识体系。全书聚焦于数字IC设计的完整流程,从抽象的系统级需求定义,逐步细化至物理实现和最终的芯片验证,强调设计方法学的演进、工具链的应用以及当前行业面临的挑战与前沿技术。 第一部分:设计流程与系统级抽象 本部分奠定了现代IC设计的基础框架。我们首先详细剖析了从概念到硅片的标准设计流程(ASIC/SoC Flow),包括设计输入、逻辑综合、布局规划、物理实现和最终的签核(Sign-off)。重点讨论了摩尔定律的现状对设计复杂度和功耗管理带来的根本性转变。 系统级建模与算法实现: 在硬件实现之前,系统行为的准确建模至关重要。本章深入探讨了使用高级语言(如SystemC或MATLAB/Simulink)进行系统级建模的方法。我们分析了如何将算法转化为可映射到硬件结构的功能块,并介绍了指令集处理器(ISA)的选择和定制化对整体系统性能的影响。这部分内容不涉及具体的高层次综合(HLS)工具的使用细节,而是关注如何从算法层面优化并行性、延迟和吞吐量,为后续的RTL设计提供最优化的功能划分。 设计约束的定义与管理: 性能、面积和功耗(PPA)是IC设计的核心指标。我们详尽讨论了如何精确定义时序约束(SDC格式的原理和应用),面积估算方法,以及功耗分析的初步框架(如静态与动态功耗的分解)。强调了在设计早期阶段,对这些约束的准确预估如何指导架构选择。 第二部分:寄存器传输级(RTL)设计与逻辑优化 RTL是连接系统级描述和门级网表之间的关键桥梁。本部分聚焦于高质量RTL代码的编写规范、模块化设计以及逻辑优化技术。 Verilog/VHDL进阶: 深入探讨了硬件描述语言(HDL)的高级特性,特别关注如何避免编写“不可综合”的代码,以及如何利用语言特性清晰地表达同步时序逻辑和组合逻辑。我们详细分析了有限状态机(FSM)的编码风格、流水线(Pipelining)技术的应用原理及其对关键路径的影响。 时序分析与逻辑综合原理: 虽然本书不讲解如何操作综合工具,但我们深入剖析了综合工具背后的逻辑。讨论了布尔代数优化、逻辑门的映射、以及如何通过逻辑重构来降低关键路径的延迟。此外,本章详细阐述了建立时间(Setup Time)和保持时间(Hold Time)违例的根本原因,以及设计者如何通过调整寄存器位置和时钟域交叉(CDC)逻辑来避免这些问题。 数据通路与控制通路设计: 重点分析了常见的数据通路结构,如算术逻辑单元(ALU)、乘法器、内存接口(如FIFO的结构)的设计细节,并讨论了如何设计高效的控制单元来管理这些数据通路的操作序列。 第三部分:物理设计与实现基础 本部分将逻辑设计转化为物理版图,侧重于后端流程的关键步骤和设计考量。 布局规划与时钟树综合(CTS): 详细分析了芯片级(Floorplanning)的策略,包括IP核的放置、电源网络的规划(Power Distribution Network, PDN)和I/O引脚的分配。对于时钟网络,本章深入探讨了为什么必须使用时钟树综合(CTS)来平衡时钟抖动(Jitter)和时钟偏移(Skew),以及不同CTS拓扑结构(如H-tree, Mesh)的优缺点。 静态时序分析(STA)深度解析: STA是签核的基石。我们不仅介绍了单沿、多沿时序检查的原理,还详细分析了工艺角(PVT)、串扰效应(Crosstalk)和上电时序(Power-Up Sequencing)对时序分析的影响。重点讲解了如何解读和修复STA报告中的关键违例。 功耗优化技术在物理实现中的体现: 探讨了在版图级别如何实施功耗降低措施,例如,电源门控(Power Gating)的设计要求、多电压域(Multi-Voltage Domain)的隔离单元(Isolation Cells)和电平转换器(Level Shifters)的原理与应用。 第四部分:验证、测试与可靠性 现代SoC设计中,验证的复杂性已远超设计本身。本部分涵盖了确保设计正确性、可制造性和长期可靠性的关键方法。 功能验证方法学: 重点介绍基于测试平台和仿真验证的传统方法,并深入探讨了更高级的验证范式,如基于约束的随机验证(CBV)和形式验证(Formal Verification)。阐述了如何构建高效的激励生成器和检查器来覆盖设计空间。 设计可测性(DFT)与测试策略: 详细讲解了芯片量产测试的必要性。深入分析了扫描链(Scan Chain)的插入、自动测试逻辑生成(ATPG)的原理,以及用于存储器测试的内建自测试(BIST)结构。强调了DFT结构如何影响设计性能和面积。 芯片可靠性与物理效应: 讨论了影响芯片长期工作稳定性的关键物理现象,包括电迁移(Electromigration, EM)、静电放电(ESD)防护的基本原理,以及闩锁效应(Latch-up)的预防措施。这部分内容帮助设计者理解物理设计选择对芯片寿命的潜在影响。 本书的结构旨在构建一个完整的、工具链无关的、专注于“为什么”和“如何实现”的设计思想体系,帮助读者驾驭日益复杂的数字集成电路设计挑战。

作者简介

目录信息

读后感

评分

评分

评分

评分

评分

用户评价

评分

评分

评分

评分

评分

相关图书

本站所有内容均为互联网搜索引擎提供的公开搜索信息,本站不存储任何数据与内容,任何内容与数据均与本站无关,如有需要请联系相关搜索引擎包括但不限于百度,google,bing,sogou 等

© 2026 book.quotespace.org All Rights Reserved. 小美书屋 版权所有