Static Timing Analysis for Nanometer Designs pdf epub mobi txt 电子书 下载 2026

- Digital_Circuits

- 非常好的书

- 工作

- STA

- IC

- Static Timing Analysis

- STA

- Nanometer Designs

- VLSI

- Digital Design

- Timing Verification

- IC Design

- Semiconductor

- Electronics

- Low Power

- Design Automation

具体描述

The book covers topics such as cell timing and power modeling; interconnect modeling and analysis, delay calculation, crosstalk, noise and the chip timing verification using static timing analysis. For each of these topics, the book provides a theoretical background as well as detailed examples to elaborate the concepts. The static timing analysis topics covered start from verification of simple blocks useful for a beginner to this field. The topics then extend to complex nanometer designs with in-depth treatment of concepts such as modeling of on-chip variation, clock gating, half-cycle paths, as well as timing of source-synchronous interfaces such as DDR. The impact of crosstalk on timing and noise is covered as is the usage of hierarchical design methodology. This book addresses CMOS logic gates, cell library, timing arcs, waveform slew, cell capacitance, timing modeling, interconnect parasitics and coupling, pre- and post-layout interconnect modeling, delay calculation, specification of timing constraints for analysis of internal paths as well as IO interfaces. Advanced modeling and analysis concepts such as controlled current source timing and noise models for nanometer technologies, power modeling including active and leakage power, crosstalk timing and crosstalk glitch calculation, verification of half-cycle and multi-cycle paths, false paths, synchronous interfaces are also covered.

作者简介

目录信息

读后感

评分

评分

评分

评分

用户评价

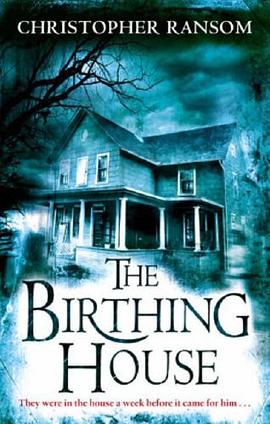

这本书的封面设计给我留下了极为深刻的印象,它采用了深邃的靛蓝色调,配以简洁而有力的白色无衬线字体,整体风格散发出一种专业和严谨的气息。初次翻阅时,我立刻被其排版的高级感所吸引。无论是页边距的留白处理,还是章节标题的字体大小和间距调整,都体现出对细节的极致追求。清晰的图表和示意性插图被巧妙地融入文本叙述之中,它们并非简单的装饰,而是作为理解复杂概念的视觉拐杖,其分辨率和线条的锐利度令人称赞,即便在复杂的时序波形分析图上,那些微小的标记和注释也纤毫毕现,这对于需要长时间盯着屏幕阅读的工程师来说,极大地减轻了视觉疲劳。同时,书本本身的装帧质量也相当扎实,纸张的选择偏向哑光处理,有效避免了阅读时常见的光线反射问题,这无疑是那些需要在实验室或拥挤工位上进行深度学习的专业人士的一大福音。这种对物理形态的重视,让我感受到作者和出版方对内容的尊重,也预示着内部知识体系的系统性与条理性,让人有理由相信其内容本身也是经过精心打磨的,绝非粗制滥造的资料堆砌。

评分这本书的配套资源和后续学习的引导性也做得非常出色,这一点常常被忽略但却至关重要。在每一章的末尾,作者都精心设计了一系列“思考题”和“扩展挑战”,这些挑战并非简单的知识点复述,而是要求读者运用本章所学知识去设计一个微型的时序验证脚本或分析一个特定的异常波形。更重要的是,书中多次提及并引用了特定的EDA工具(如主流厂商的时序分析引擎)的命令行接口(CLI)参数和脚本语法,这表明作者在撰写时,是直接基于行业标准工具链进行内容验证的,而非仅仅停留在理论推演层面。这使得读者在合上书本,准备进行实际操作时,能够迅速找到“入口点”,将书本上的理论知识无缝转化成可执行的EDA脚本和验证环境。这种对工程实用性的极致聚焦,确保了这本书不仅仅是一本可以放在书架上落灰的理论宝典,而是一个真正能够在芯片开发生命周期中反复查阅的实战指南。

评分这本书的语言风格极其鲜明,它不像某些教科书那样充满了生涩的数学推导和晦涩的学术腔调,反而更像是一位经验极其丰富的资深首席工程师在向初级工程师进行一对一的“导师指导”。叙述的逻辑推进是渐进式的,但每一步都建立在坚实的基础之上,绝不跳跃。例如,在讨论关键路径的敏感度分析时,作者首先用了一个非常直观的比喻——“时序路径就像一条水管,水流速度(时序裕量)受限于最细的那段瓶颈”,随后才引入复杂的二次偏导数公式,这种“先建立直觉,后量化验证”的教学路径,极大地降低了初学者对高阶概念的畏惧感。更难得的是,作者在关键的公式推导旁,经常穿插一些简短的、带有个人色彩的“经验之谈”或“陷阱警告”,这些批注往往一语中的,直接指出了新手在实际EDA工具仿真中容易忽略的软件设置偏差或工具模型差异,这种沉淀了多年实战教训的“软信息”,对于快速提升实战能力具有无可估量的价值。

评分我对书中关于集成电路制造工艺(Process Variation)与时序分析结合的部分给予高度评价。在纳米级设计中,工艺偏差不再是一个可以被简单地用裕量覆盖掉的“黑盒”问题,而是时序分析的核心挑战之一。此书没有将工艺变化视为一个固定的参数集,而是将其置于整个设计流程的动态环境中进行考察。它详细剖析了不同制造批次(Lot-to-Lot)和同一晶圆内不同区域(Within-Die)的延迟差异如何以非线性方式影响到全局时序的稳定性。书中对SRAM单元的访问时间在极端工艺角下的统计建模方法,展示了作者对半导体物理的深刻理解,不仅仅停留在Verilog-A模型层面,而是追溯到了晶体管的阈值电压和沟道长度调制效应的影响机制。这种由底层物理向高层设计规则层层渗透的分析框架,使得读者可以真正理解“为什么”需要如此严格的时序约束,而非仅仅机械地遵守它们。这对于那些立志于成为芯片架构师而非仅仅是布局布线工程师的人士来说,是不可或缺的知识深度。

评分我花费了大量时间来研究书中关于跨时钟域(CDC)处理的部分,发现其阐述的角度极其新颖且富有实践指导性。传统的教材往往停留在同步器结构的基本介绍,但这本书却深入探讨了在当前先进工艺节点下,异步信号在亚纳秒级延迟变化背景下的“隐形”时序风险。作者不仅仅罗列了已知的握手协议,更是用一种近乎建筑师般的视角,构建了不同同步策略的“时序安全边界模型”。特别是对多比特数据总线的延迟不匹配问题的剖析,书中展示了一套通过增加冗余位和引入特定的采样窗口来动态补偿相位误差的定制化方法,这套方法论远超我之前接触的任何公开文档或企业内部培训资料的深度。阅读过程中,我不得不频繁地停下来,对照我目前负责的芯片设计中的某个模块进行反思和对照,那种豁然开朗的感觉,仿佛是长期困扰我的一个技术瓶颈突然被一把锋利的工具切开,清晰地显露出其内在的结构。这种从理论高度抽象、到工程实践落地的无缝衔接能力,是衡量一本优秀技术专著的关键标准,而此书在这方面表现得淋漓尽致。

评分Read during work to learn about STA

评分非常好的书

评分非常好的书

评分Read during work to learn about STA

评分非常好的书

相关图书

本站所有内容均为互联网搜索引擎提供的公开搜索信息,本站不存储任何数据与内容,任何内容与数据均与本站无关,如有需要请联系相关搜索引擎包括但不限于百度,google,bing,sogou 等

© 2026 book.quotespace.org All Rights Reserved. 小美书屋 版权所有